- #U boot configuration how to

- #U boot configuration generator

- #U boot configuration manual

- #U boot configuration pro

They can still be set in the interface, but they have no effect

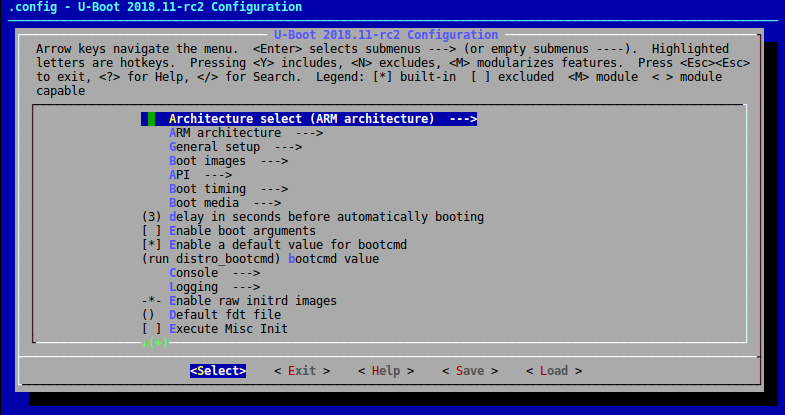

For older versions of SoC EDS, the user could set various U-Boot parameters in bsp-editor. Bsp-editor takes this information and turns it into source code which is used to build U-Boot. See doc/README.socfpga for Quartus and Device support.įor Cyclone V SoC and Arria V SoC, the handoff information created by Quartus compilation comes in several formats: C source code, XML and binary files.Latest stable branch (no RC labeled) is strongly recommended for development and production use outside of Intel.A "RC" labeled branch is for internal active development use and customer early access without official customer support.The official Intel SOCFPGA U-Boot repository is located at. For Arria 10, the bsp-editor functionality was incorporated in an U-Boot script, and the tool is not needed anymore.

#U boot configuration pro

Starting with Quartus Pro 20.3, the SoC EDS was discontinued, and the functionality of the tools which were previously part of SoC EDS are provided separately. Note that Arria V SoC flow is identical with the Cyclone V SoC one, so it is not presented separately.

#U boot configuration how to

Instead the user is notified about this page, which contains instructions on how to build the bootloader. Does not create a makefile which builds the bootloader.Instead all custom user settings must be done directly in U-Boot (device tree, configuration and source code). Does not support custom user settings anymore.

#U boot configuration generator

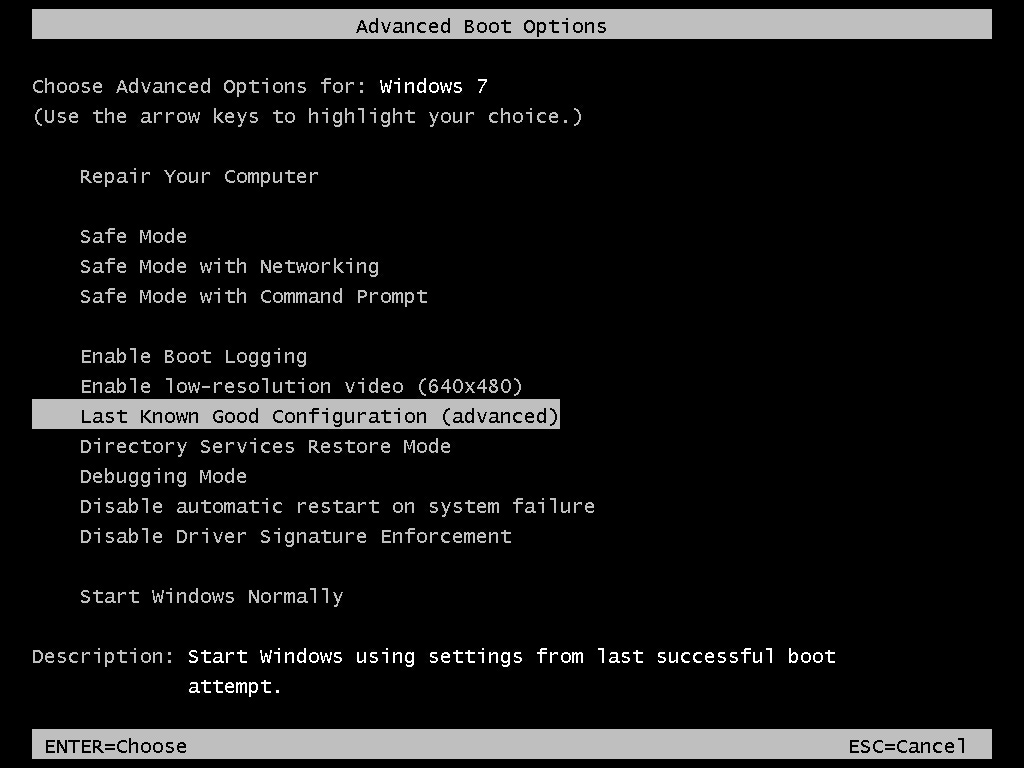

Note: SoC EDS is no longer required to generate the handoff folder for Cyclone V for releases 22.1std and after. This page contains instructions on how to build U-Boot in the following configurations: Appendix - Customizing Arria 10 GHRD Recipes for Custom Board.Appendix - Debugging U-Boot with Arm DS Eclipse.Arria 10 SoC - Run U-Boot from Debugger.Cyclone V SoC - Run U-Boot from Debugger.Appendix - Running U-Boot with the Debugger from Command Line.Option #2 - Combined Configuration File.Option #1 - Separate Configuration Files.

#U boot configuration manual

0 kommentar(er)

0 kommentar(er)